The 12bit resolution ADC is suitable for next-generation wireless LANs while the circuits power efficiency is the world’s highest, three times that of current ADCs, Toshiba claimed.

The company has presented a paper on the circuit at the International Solid-State Circuits Conference in San Francisco. The circuit is a 0.7V, 12bit resolution successive approximation register ADC that operates at up to 120Msamples/s with an energy consumption of 12.8fJ per conversion. It has been implemented in 28nm CMOS.

Target speeds for wireless LANs continue to increase and one key to achieving that is higher conversion accuracy which it tunr depends on higher multiplication accuracy in the amplifiers of the ADC. By conventional methods that would increase power consumption in the op amp and result in a trade-off between conversion accuracy and power efficiency.

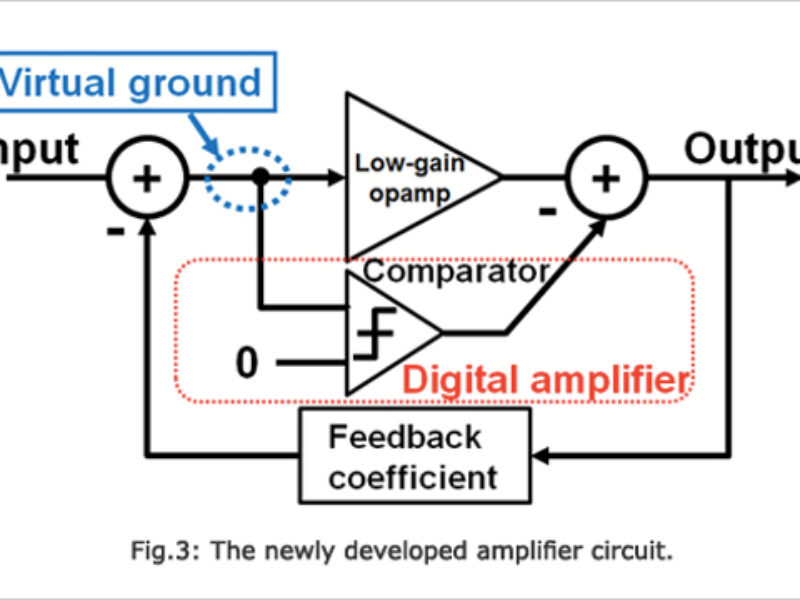

Toshiba has used the idea of a floating or “virtual ground” to improve multiplication accuracy and adding a comparator to detect the virtual ground voltage and a controlling amplifier to manipulate it.

The digital amplifier mostly comprises digital circuits that consume less power than analog circuits, because power-hungry op amps are eliminated and current flows only when the signals switch. Furthermore, digital amplifier performance can be improved greatly by CMOS scaling, which simultaneously lowers manufacturing costs.

Related links and articles:

News articles:

Linear Technology: 24-Bit 2Msps SAR ADC

DARPA funds novel ADC architecture development

S3 claims smallest, most efficient 12bit SAR ADC, again

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News