Tachyum sues Cadence for $211m over failed IP

European processor designer Tachyum is suing Cadence Design Systems in the US for $211m over failed memory and interface IP blocks.

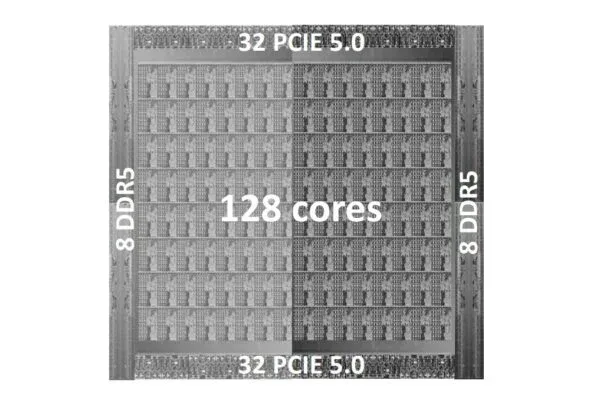

Tachyum is developing a universal processor that can handle the operations of a CPU, GPU and AI accelerator in the same chip. The chip as 128 cores and is aimed at data centres and supercomputers, using 64 PCI Express (PCIe) 5.0 interfaces and 16 DDR5 memory interfaces.

Related Tachyum articles

- Tachyum plans 3nm Universal processor

- Tachyum teams for German supercomputer

- Slovakia aims to build world’s fastest AI supercomputer

The Prodigy design project should have taped out last year on a 5nm process, but was severely delayed as there were issues with the PCIe and DDR5 memory interface IP blocks.

“We purchased IP for the DDR5 memory and PCIe and the supplier had an issue,” said Radoslav Danilak, founder and CEO of Tachyum told eeNews Europe previously. “We replaced that with Rambus and AlphaWave and another for DDR5. That was a nasty surprise but the good news is that the new IP is integrated and ready now.”

In a court case filed in Santa Clara, California, the supplier of these block is identified as Cadence. Cadence declined to comment. “Cadence does not comment on pending legal proceedings,” it said.

The deal was significant, with the contracts with Cadence totalling a quarter of the funds Tachyum has raised to date, which is $42m according to Crunchbase. While the deal may have been worth up to $10m, it appears around $5m was paid, although this is redacted in the court papers.

“For nearly two years, Tachyum tried to work with Cadence to find solutions to these problems despite the persistent and widespread project delays and frustrations,” says the lawsuit. “Tachyum’s heavy investment in the Cadence relationship, both monetarily and technologically, meant it would not be a simple matter to switch to different vendors and service providers. Ultimately, however, Tachyum determined it had no choice.”

Part of the problem was the lock-in to the Cadence design tools and the time needed to shift to tools from other suppliers.

Rambus is now supplying its PCI Express (PCIe) 5.0 IP, while UK-based Alphawave is supplying its AlphaCORE Long-Reach (LR) Multi-Standard-Serdes (MSS) PHY with speeds up to 112Gbps.

Tachyum is asking for the money spent on the contract, which is up to $10m, with least another $206m “in increased expenses and lost profits caused by Cadence’s wrongful conduct,” it said.

This is a result of missing out on projects such as the MareNostrum 5 being developed by the Barcelona Supercomputing Centre (BSC) in Spain, which would have been worth €151m. The delay also meant missing out on orders of at least $20m, says the complaint.

The next generation Prodigy 2 design will be built on a 3nm process and add the CXL memory interface and PCIe 6.0 lanes from the same IP suppliers and increase the number of cores. The plan is for samples of this chip in 2024.

www.tachyum.com; www.cadence.com

Other articles on eeNews Europe

- Battle of the multilayer flash chips

- Analyst warns of China threat to global telecoms over Taiwan

- Analyst warns semiconductor downturn has started

- Committee calls for urgent UK science plan

- Nordic Semi sets up RISC-V design team

- UK police use AI to detect phone users in cars

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News