CEO interview: Minima’s Tuomas Hollman on why static timing sign-off is over

We asked Hollman to tell us how the company would be using its recently announced European funding (see Europe invests €227m directly in tech startups) and he shared his opinion on why circuit design has to change. He said: “Static timing sign-off is over.”

Minima Processors was founded in 2016 following a resurgence of interest in sub- and near-threshold voltage operation of circuits. Transistor power consumption is related to the square of the voltage of operation so reducing the voltage produces a square-law benefit. The disadvantage is that signal transitions are slowed and therefore in clocked digital logic the maximum clock frequency has to be reduced. It’s a trade-off but one that often produces an overall benefit and this has been exploited in specialist circuits, such as in electronic watch circuits, since the 1970s.

However, the devil is in the detail and in the fabless-foundry world transistor and standard cell models are usually only characterized at well above threshold voltage. This makes the route to market for fabless chip companies more complex in terms of risk than conventional design using standard cells and IP cores, as given.

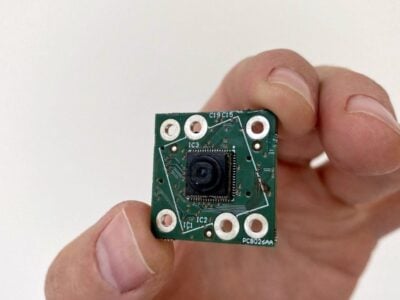

In its early years Minima was involved in a couple of designs as demonstrators of the power savings achievable. One was a Cortex-M3 microcontroller and the other a CoolFlux DSP (see Minima, ARM apply ‘real-time’ voltage scaling to Cortex-M3 and Minima to offer NXP’s CoolFlux DSP in near-threshold form). The company claims it can achieve greater than 60 percent energy savings for SoC circuits based on its approach.

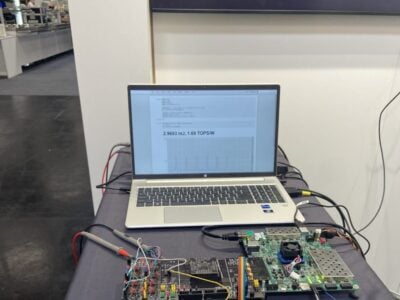

Silicon validated results of Minima near-threshold design applied to SoC circuits. Source: Minima Processor

Hollman said: “However, hard macros often don’t cut it.” Hollman found Minima was doing a lot of custom SoC circuits and design support for high volume application-specific processors. Battery-operated wearables and hearables have been fertile ground for Minima’s SoC approach. “We needed to adapt our offering to that,” he said.

Next: EDA, IP, design service

Hollman acknowledges that electronic design support activity often lies in a plane defined by three poles: Intellectual property as circuits for license is one pole; design services is another; and the third is EDA software tools. IP cores and EDA tools are the most product-like offerings, and they are often preferred business models due to their scalability. Design support is tied to engineering resources and so does not scale well. But many design support companies end up in the middle of that plane, doing a bit of all three activities.

To help with near-threshold circuit design Minima has its own internal tools and it plans to use its European accelerator money to productize those tools and to help its customers be able to do more of their own low-voltage design, Hollman said.

Hollman said that under the European accelerator scheme Minima was selected for “blended” finance, which means a combination of a grant and equity funding. The grant is worth €2.4 million (about US$2.7 million) and the equity co-investment worth up to €5 million (about US$5.6 million). The exact size of the equity investment and its terms are still to be negotiated.

This is useful money for the 15-person company and it comes on top of investment led by TESI in 2020 and another investment round in progress. But perhaps this is necessary funding because Minima hasn’t been that prominent to date?

Hollman points out that when you are working in the custom space, clients often want to keep their market advantage quiet, which makes it hard for a supplier such as Minima to proclaim its successes.

Hollman said that the company has worked on multiple bulk CMOS nodes with the two leading Taiwanese foundries – TSMC and UMC. These have included: 55nm, 40nm, 28nm and 22nm nodes.

He added that in the financial year that closed at the end of September 2021, customer revenue was up more than 80 percent over the previous year. He said the company has experience with all the major processor IP core architectures and was a founding member of the RISC-V organization. And Minima has signed a second consecutive project with a customer active in wearables and Edge-AI SoCs.

Hollman said the company wants to triple headcount over the next couple of years and to become profitable by early 2024.

Next: A broader advantage

Hollman said there is a particular detail of Minima’s form of near-threshold voltage operation design style that could provide a broader advantage in the market place. And this is the use of “dynamic margining.” This can be thought of as an additional layer of sophistication above and beyond the periodic dynamic voltage and frequency scaling (DVFS) which is now fairly standard circuit design approach in processor SoCs.

The essential difference in the Minima approach is real-time dynamic margining for power. It does this on a very fine-grained basis.

Minima provides both hardware and software to enable circuits to modify power usage during operation in response to performance needs, process variations, or environmental conditions in real time. Minima inserts timing and voltage monitors along paths to monitor power and performance during operation. If a critical path monitor is activated by a voltage drop, for whatever reason, then software and dynamic feedback responds by temporarily slowing the path for a clock cycle, or until conditions allow a resumption of previous performance.

“In our latest designs, we actually use the monitoring to maintain the performance by quickly responding with the correct supply voltage. So, if circuitry performance drops for whatever reason, then our solution immediately adjusts the voltage to guarantee the required performance,” said Hollman.

The OS-controlled middleware adjusts to conditions. Instead of operating based on worst-case assumptions, Minima lets the circuit run as quickly as possible at a given voltage and only slows operations or increases voltage when necessary – and only for as long as necessary.

This is unlike static approaches that seek to make a gate library completely robust for low-power operation. The Minima dynamic-margining approach makes sure the operating conditions are correct in real-time. This allows Minima to use ordinary gate libraries that are only re-characterized for low voltage, and then near-threshold operation – a much lighter process than a full library makeover.

It is notable that since about 2016 TSMC and other foundries have been producing such low-voltage manufacturing processes and TSMC 22ULL is one of the nodes where Minima has gained experience.

Next: An EDA tool suite

“Our customers have all used the dynamic optimization as a fundamental part of the offering,” said Hollman. “Internally, what we do is highly automated. We have worked hard to make that deliverable as standard EDA that easily transfers node-to-node.” Hollman continued: “We would still do early work but more of the implementation could be owned by the customer.”

The plan is to provide a dynamic optimization delivery kit in 2023 and to follow that up with a full EDA tool suite, said Hollman.

But the utility of dynamic margining is broader, Hollman said. “It comes back to the claim that static timing sign-off is over.” He added: “TSMC has lower voltage libraries, but [as you go down in voltage or geometry] you still hit the variance. What can I do about that?”

The variance Hollman speaks of can include process variation in transistor length and width, metal thickness variation due to chemical mechanical polishing, line edge roughness and gate oxide thickness. Then there are environmental variations such as voltage and temperature. All this has been well-known for decades and the classical design solution is to model these variations statistically and apply margins to design for the worst-case.

But Hollman’s point is that as voltages and geometries decrease the variations are becoming much more significant and the margins to prevent the possibility of circuit failure are becoming so large they negate the incentive to go to smaller nodes or lower voltages.

Next: At 28nm AND at 3nm

“There is a strong parallel in edge devices designed at 28nm and below for extremely energy-sensitive applications. In 5nm and 3nm design the challenge is parallel. The supply voltage is coming down but the threshold voltage is not, so the variation is increasing,” said Hollman.

There is an historical ‘worst-case engineering’ design paradigm that may take some effort to shift. But characterizing complete suites of libraries and IP cores across multiple process nodes and then having to provide guard-band margins for circuits to guarantee correct operation against all possible operating conditions and circumstance is expensive and is producing diminishing returns.

Minima’s way is to design circuits in a more relaxed way and then let dynamic margining keep the circuit operating at the optimum point in real time.

“Dynamic margining is a tremendous alternative to statistical modelling and leaving big margins in circuits. Dynamic margining has to happen in every device,” Hollman asserted.

This may make Minima Processor more of an EDA company in the future but definitely a company to watch as near-threshold voltage operation moves from the hearing aid and ear bud and into the smartphone and edge-AI device.

Related links and articles:

News articles:

Europe invests €227m directly in tech startups

Minima, ARM apply ‘real-time’ voltage scaling to Cortex-M3

Minima to offer NXP’s CoolFlux DSP in near-threshold form

Finnish sub-threshold startup raises additional funds

Sub-threshold processor startup gets funds

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News